您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這篇文章主要介紹了Verilog循環語句實例分析的相關知識,內容詳細易懂,操作簡單快捷,具有一定借鑒價值,相信大家閱讀完這篇Verilog循環語句實例分析文章都會有所收獲,下面我們一起來看看吧。

關鍵詞:while, for, repeat, forever

Verilog 循環語句有 4 種類型,分別是 while,for,repeat,和 forever 循環。循環語句只能在 always 或 initial 塊中使用,但可以包含延遲表達式。

while 循環語法格式如下:

while (condition) begin … end

while 循環中止條件為 condition 為假。

如果開始執行到 while 循環時 condition 已經為假,那么循環語句一次也不會執行。

當然,執行語句只有一條時,關鍵字 begin 與 end 可以省略。

下面代碼執行時,counter 執行了 11 次。

實例

`timescale 1ns/1ns module test ; reg [3:0] counter ; initial begin counter = 'b0 ; while (counterb1 ; end end //stop the simulation always begin #10 ; if ($time >= 1000) $finish ; end endmodule

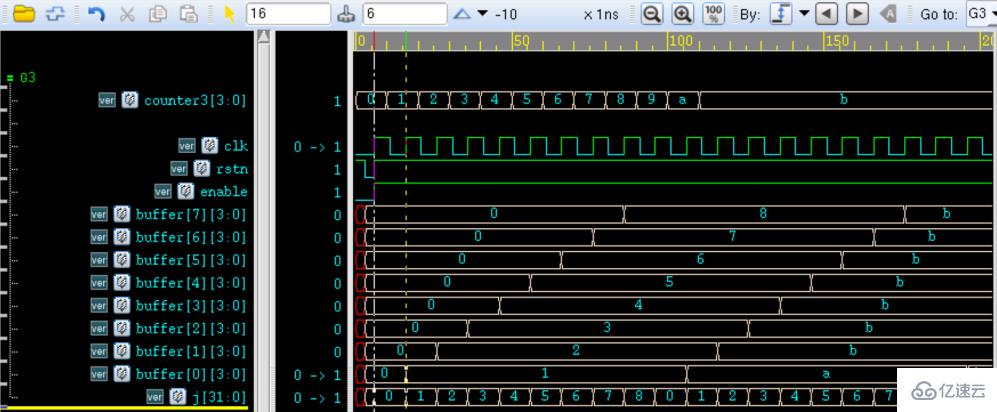

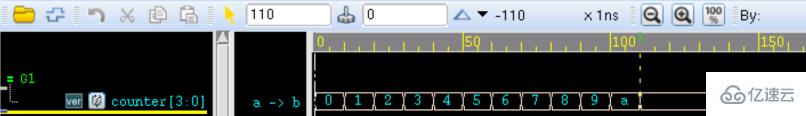

仿真結果如下:

for 循環語法格式如下:

for(initial_assignment; condition ; step_assignment) begin … end

initial_assignment 為初始條件。

condition 為終止條件,condition 為假時,立即跳出循環。

step_assignment 為改變控制變量的過程賦值語句,通常為增加或減少循環變量計數。

一般來說,因為初始條件和自加操作等過程都已經包含在 for 循環中,所以 for 循環寫法比 while 更為緊湊,但也不是所有的情況下都能使用 for 循環來代替 while 循環。

下面 for 循環的例子,實現了與 while 循環中例子一樣的效果。需要注意的是,i = i + 1 不能像 C 語言那樣寫成 i++ 的形式,i = i -1 也不能寫成 i — 的形式。

實例

// for 循環語句integer i ; reg [3:0] counter2 ; initial begin counter2 = 'b0 ; for (i=0; ib1 ; end end

repeat 循環語法格式如下:

repeat (loop_times) begin … end

repeat 的功能是執行固定次數的循環,它不能像 while 循環那樣用一個邏輯表達式來確定循環是否繼續執行。repeat 循環的次數必須是一個常量、變量或信號。如果循環次數是變量信號,則循環次數是開始執行 repeat 循環時變量信號的值。即便執行期間,循環次數代表的變量信號值發生了變化,repeat 執行次數也不會改變。

下面 repeat 循環例子,實現了與 while 循環中的例子一樣的效果。

實例

// repeat 循環語句 reg [3:0] counter3 ; initial begin counter3 = 'b0 ; repeat (11) begin //重復11次 #10 ; counter3 = counter3 + 1'b1 ; end end

下面 repeat 循環例子,實現了連續存儲 8 個數據的功能:

實例

always @(posedge clk or negedge rstn) begin j = 0 ; if (!rstn) begin repeat (8) begin buffer[j] 'b0 ; //沒有延遲的賦值,即同時賦值為0 j = j + 1 ; end end else if (enable) begin repeat (8) begin @(posedge clk) buffer[j]

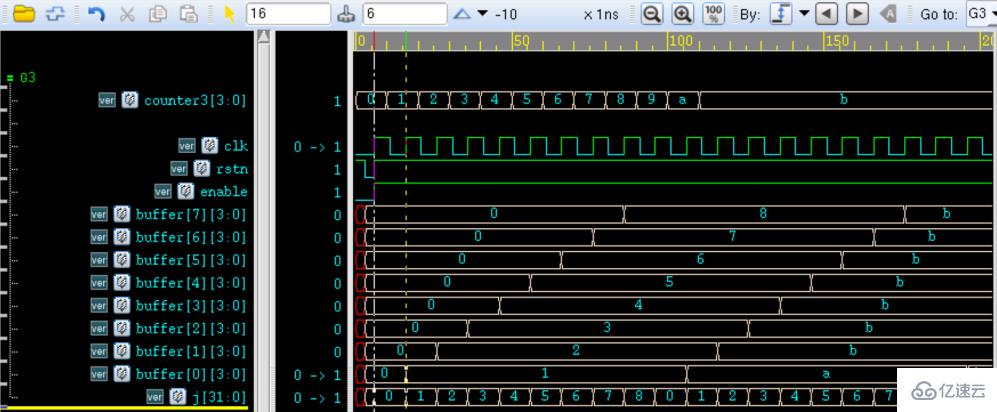

仿真結果如下圖。

由圖可知,rstn 拉高時,buffer 的 8 個向量同時賦值為 0。

第二個時鐘周期后,buffer 依次被 counter3 賦值,實現了連續存儲 8 個數據的功能。

forever 循環語法格式如下:

forever begin … end

forever 語句表示永久循環,不包含任何條件表達式,一旦執行便無限的執行下去,系統函數 $finish 可退出 forever。

forever 相當于 while(1) 。

通常,forever 循環是和時序控制結構配合使用的。

例如,使用 forever 語句產生一個時鐘:

實例

reg clk ; initial begin clk = 0 ; forever begin clk = ~clk ; #5 ; end end

例如,使用 forever 語句實現一個時鐘邊沿控制的寄存器間數據傳輸功能:

實例

reg clk ; reg data_in, data_temp ; initial begin forever @(posedge clk) data_temp = data_in ; end

關于“Verilog循環語句實例分析”這篇文章的內容就介紹到這里,感謝各位的閱讀!相信大家對“Verilog循環語句實例分析”知識都有一定的了解,大家如果還想學習更多知識,歡迎關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。