您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

這期內容當中小編將會給大家帶來有關如何進行IO管腳約束,文章內容豐富且以專業的角度為大家分析和敘述,閱讀完這篇文章希望大家可以有所收獲。

IO管腳約束是FPGA設計上板驗證的必需環節,它們會對布局布線和時序造成影響。有三種方式來進行管腳約束,一種是通過VIvado管腳約束界面,一種是通過命令行,還有一種可以導入CSV文件。

1. 可視化界面方式

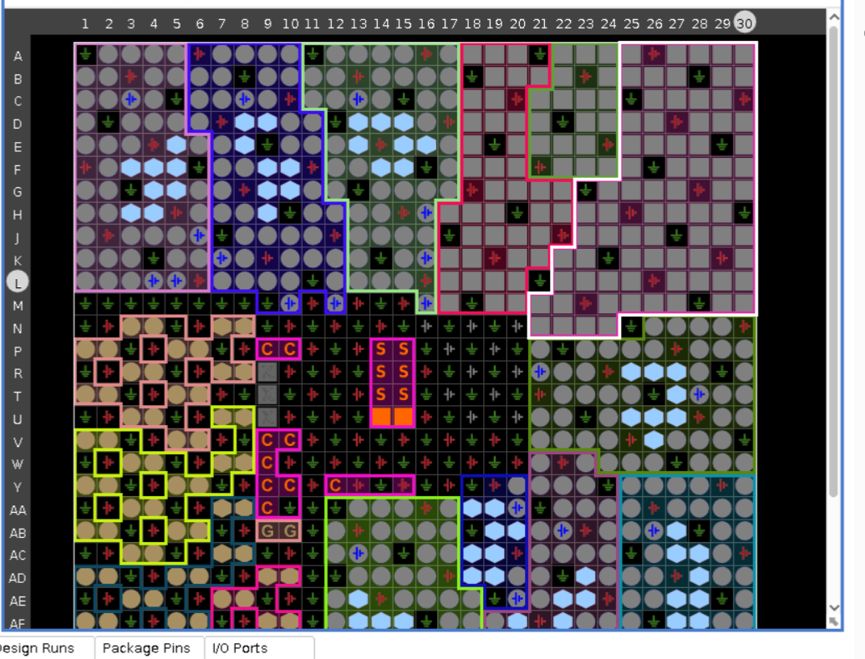

當完成了綜合之后,可以打開綜合界面,這個時候可以在layout下看到IO planning,打開就是IO約束界面。界面中可以顯示設計頂層的IO管腳,同時我們還可以看到芯片中管腳的分布圖。列方向的編號是用大寫字母,從最左上角A開始,橫向是數字排列,從1開始。不同顏色的區域代表不同的時鐘域(IO bank)。不同的IO bank提供的引腳功能是有區別的,有的IO bank可能提供高速差分信號,有的提供低電壓引腳,用戶可以靈活的根據需求使用。分配引腳首先就需要分辨出哪些是普通引腳,哪些是時鐘引腳。從界面中可以看出六邊形的都是時鐘引腳,圓形的是普通引腳。進一步放大還可以看出引腳有N,P可以用于差分。

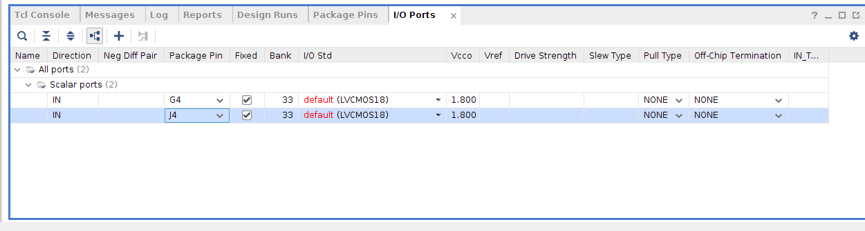

接下來我們可以在io ports中選擇引腳。如何我們選擇保存,可以將管腳約束保存成xdc文件。

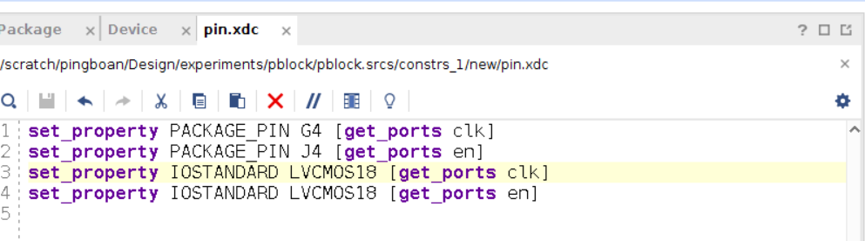

2. 使用xdc文件進行約束

Set_property來定義管腳屬性,get_ports獲得管腳名稱。這里邊一個是選擇了引腳名稱,另外一個設置電壓,這兩種是經常用到的。

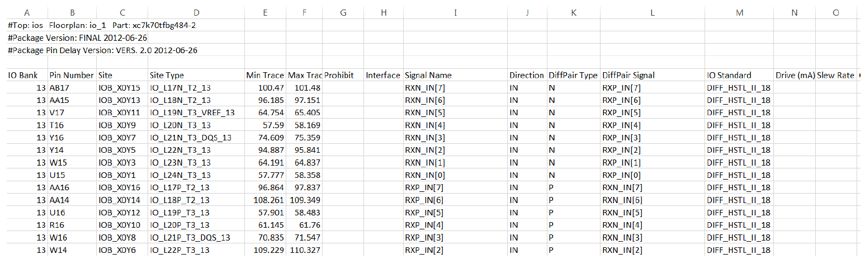

3. 導入CSV文件。

CSV是一種用于FPGA管腳約束的標準文件,看起來是以表格形式顯示出來的,非常簡潔。其中定義了IO bank,pin number,IO standard等屬性。用戶根據需要進行填寫就行。

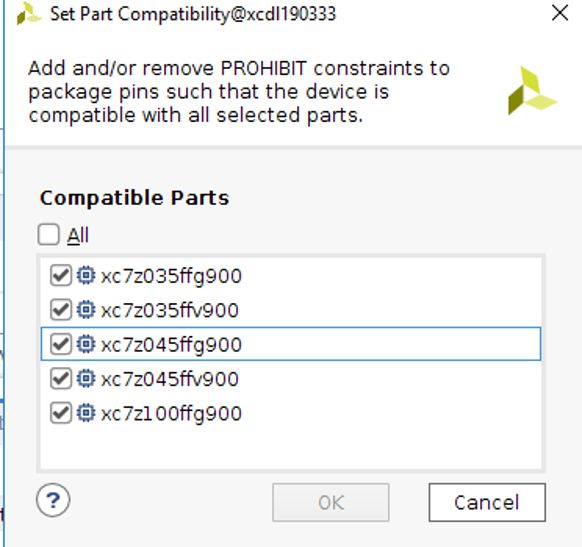

Vivado還提供了芯片兼容性管腳提示,對于引腳封裝相同的芯片,工具為我們提供可以同時來兼容這些芯片的引腳分配功能,選擇tools中的IO planning->set part compatibility我們可以看到具有相同封裝的芯片,我們可以根據后續更改芯片需要來選擇。選擇后,工具會提示我們哪些管腳不是所有芯片公用的,哪些是可以同時兼容的。不能公用的會顯示prohibit圖標。

上述就是小編為大家分享的如何進行IO管腳約束了,如果剛好有類似的疑惑,不妨參照上述分析進行理解。如果想知道更多相關知識,歡迎關注億速云行業資訊頻道。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。