您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

本篇內容介紹了“Vivado怎么生成HDL例化模板”的有關知識,在實際案例的操作過程中,不少人都會遇到這樣的困境,接下來就讓小編帶領大家學習一下如何處理這些情況吧!希望大家仔細閱讀,能夠學有所成!

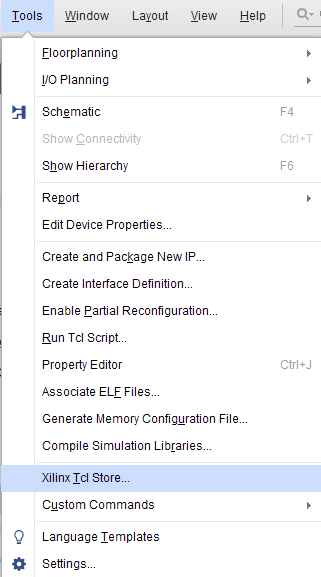

首先要安裝Design Utilities, 點擊Tools->Xilinx Tck Store選項,如下圖1所示。

圖 1.

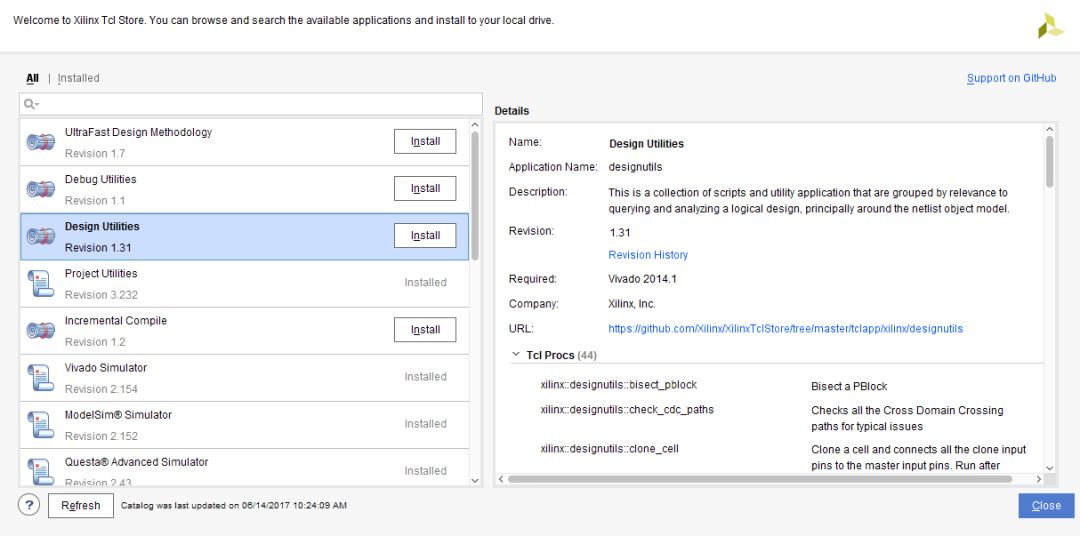

點擊Install, 安裝Design Utilities,如下圖2所示。

圖 2.

之后再生成例化模板時就不需要再安裝了,直接進行下面的步驟就行。

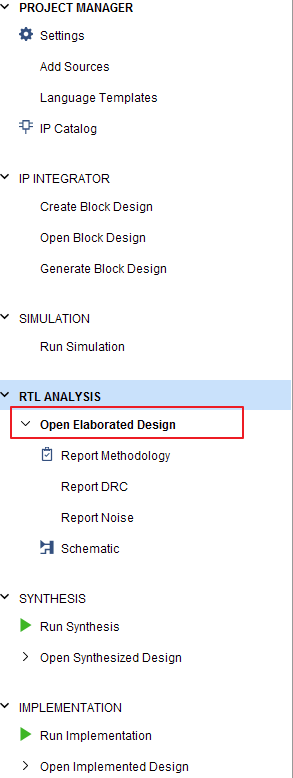

把要生成例化模板的HDL文件設置為top文件,并點擊Open Elaborated Design,如下圖3所示。

圖 3.

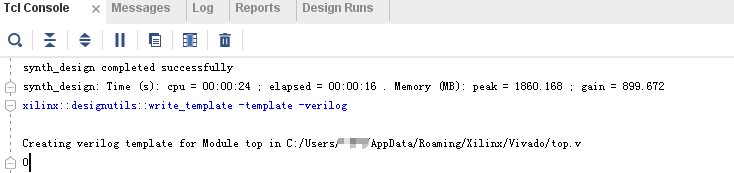

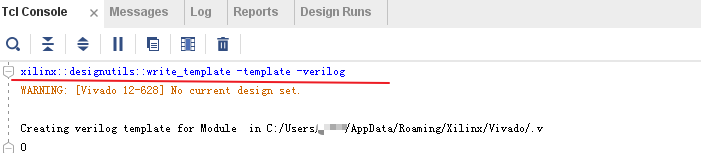

在Tcl Console中執行xilinx::designutils::write_template -template -verilog指令,就可以看到下圖4所示,根據提示內容,去對應位置找到生成的例化模板文件即可。

圖 4.

如果沒有執行第3步操作,就會出現下面的情況

圖 5.

可以看出,提示了Warning,并且生成了一個沒有名字的.v文件。如果打開文件的話,會發現文件中并沒有有用內容。

好,到這里,就已經正確生成了HDL例化模板了。但每次都需要輸入tcl指令還是略顯麻煩,我們可以設置一個tcl的按鈕,一鍵生成。操作如下:

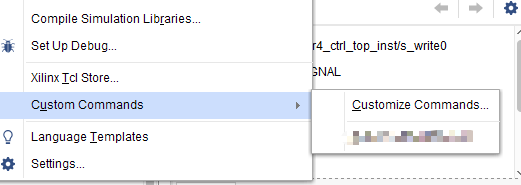

點擊Tools->Custom Commands->Customize Commands,如下圖6所示。

圖 6.

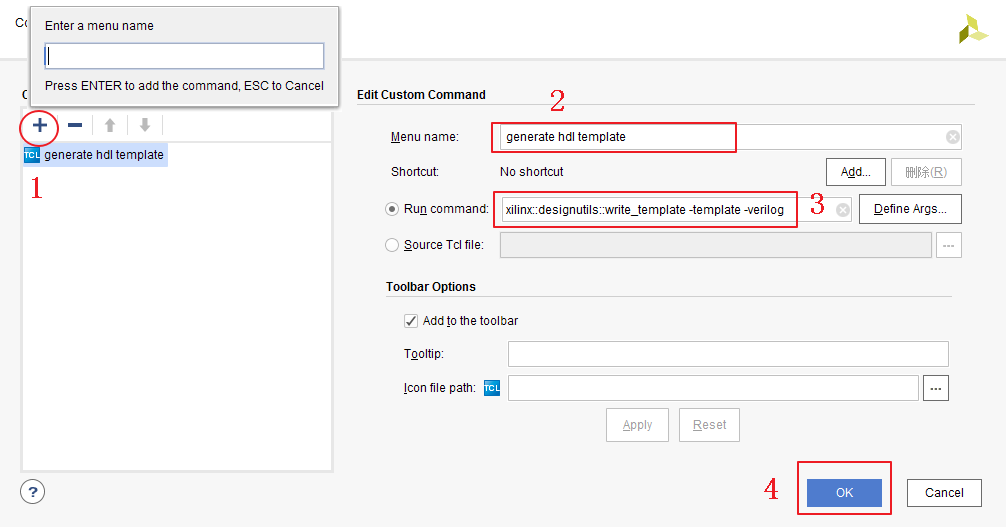

進去之后,按照下圖的操作步驟,生成tcl指令。

圖 7.

操作完后,就可以在vivado的菜單欄中看到tcl的按鈕標志,如下圖8所示。

圖 8.

以后在敲指令的步驟就可以替代為直接點擊該按鈕即可。

“Vivado怎么生成HDL例化模板”的內容就介紹到這里了,感謝大家的閱讀。如果想了解更多行業相關的知識可以關注億速云網站,小編將為大家輸出更多高質量的實用文章!

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。