溫馨提示×

您好,登錄后才能下訂單哦!

點擊 登錄注冊 即表示同意《億速云用戶服務條款》

您好,登錄后才能下訂單哦!

1. VGA概述

VGA(Video Graphics Array)是IBM在1987年推出的一種視頻傳輸,具有分辨率高、顯示速率快、顏色豐富等優點,在彩色顯示器領域得到了廣泛的應用。不支持熱插拔,不支持音頻傳輸。

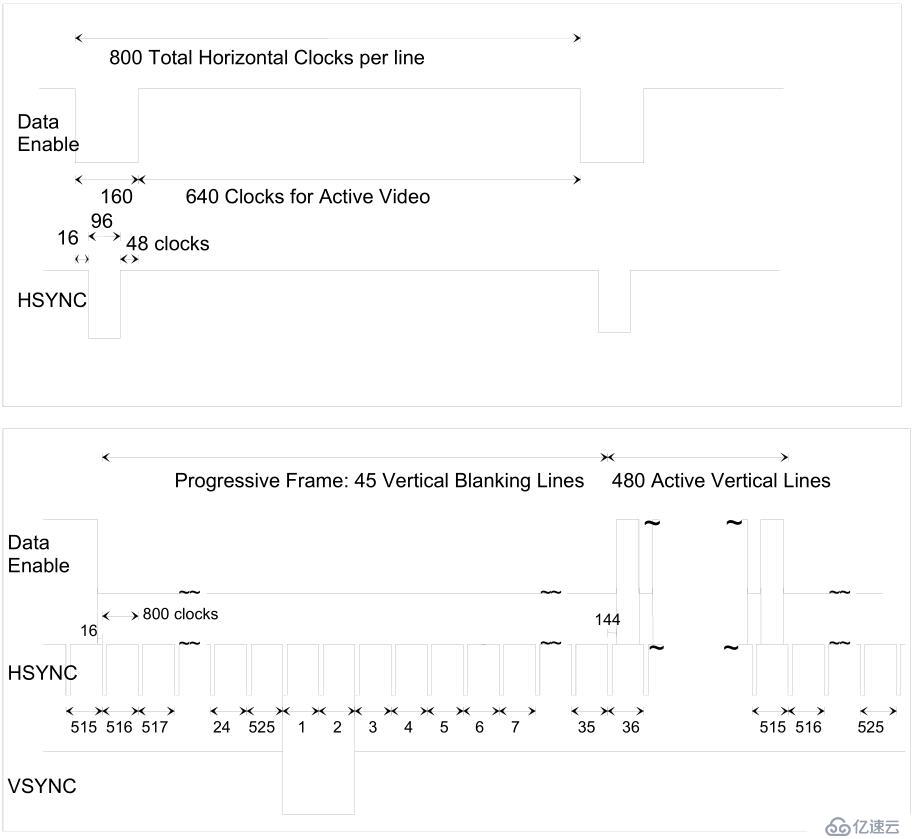

2. VGA時序

下面以640*480@60Hz為例說明VGA時序和FPGA設計,其他分辨率和幀率的可參考VESA中查找。

計算像素時鐘pclk = 800*525*60 = 25200000,注意這里的HSYNC和VSYNC都是低電平有效,且HSYNC在數據行無效區域也要提供。

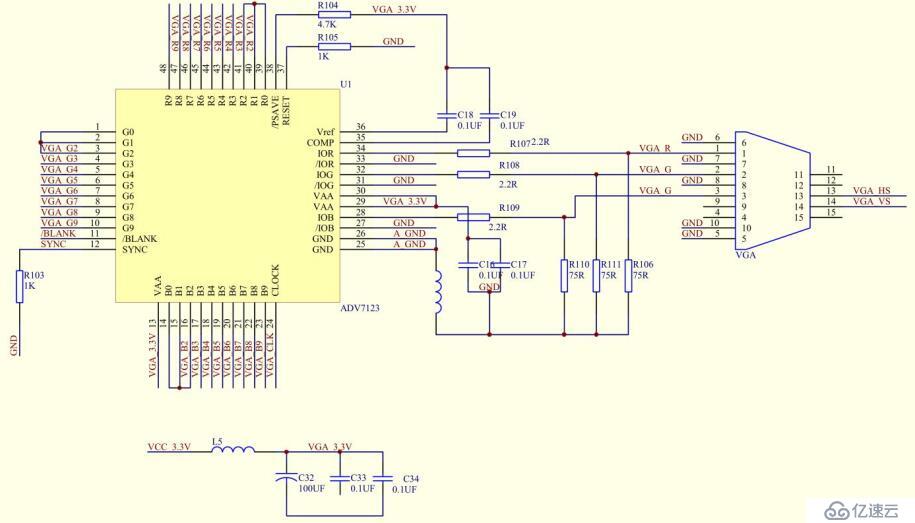

3. VGA電路圖

電路以ADV7123為例:

4. FPGA邏輯代碼

//------------Video Test--------------- parameter IMG_HDISP =16'd640; parameter IMG_VDISP = 16'd480; wire pclk; assign pclk = clk_25m; //VIDEO input reg [15:0] vcnt; reg [11:0] hcnt; reg vsync; reg hsync; reg [7:0] data; reg data_valid; always @(posedge pclk) if(hcnt>=(IMG_HDISP+159)) hcnt <= 0; else hcnt <= hcnt + 1'b1; always @(posedge pclk) if(hcnt>=(IMG_HDISP+159)) if(vcnt>=(IMG_VDISP+44)) vcnt <= 0; else vcnt <= vcnt + 1'b1; else vcnt <= vcnt; always @(posedge pclk) if((hcnt>=IMG_HDISP+16) & (hcnt<(IMG_HDISP+96)))// & (vcnt>=0) & (vcnt<(IMG_VDISP))) hsync <= 1'b1; else hsync <= 1'b0; always @(posedge pclk) if(vcnt>=(IMG_VDISP+9) & vcnt<(IMG_VDISP+11)) vsync <= 1'b1; else vsync <= 1'b0; always @(posedge pclk) if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=0) & (vcnt<(IMG_VDISP))) data_valid <= 1'b1; else data_valid <= 1'b0; always @(posedge pclk) if(vsync) data <= 0; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=0) & (vcnt<(IMG_VDISP/4))) // data <= data + 1'b1; if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'h00; else data <= 8'hff; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(IMG_VDISP/4)) & (vcnt<(2*IMG_VDISP/4))) if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'hff; else data <= 8'h00; // data <= data + 1'b1; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(2*IMG_VDISP/4)) & (vcnt<(3*IMG_VDISP/4))) if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'h00; else data <= 8'hff; // data <= data + 1'b1; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(3*IMG_VDISP/4)) & (vcnt<(IMG_VDISP))) // data <= data + 1'b1; if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'hff; else data <= 8'h00; else data <= 0; assign lcd_vs = ~vsync; assign lcd_hs = ~hsync; assign vga_red = data; assign vga_green = data; assign vga_blue = data; assign lcd_dclk = clk_25m; assign lcd_blank = 1'b1; assign lcd_sync = 1'b0; wire [7:0] vga_red; wire [7:0] vga_green; wire [7:0] vga_blue; assign lcd_red[9:2] = vga_red; assign lcd_green[9:2] = vga_green; assign lcd_blue[9:2] = vga_blue;

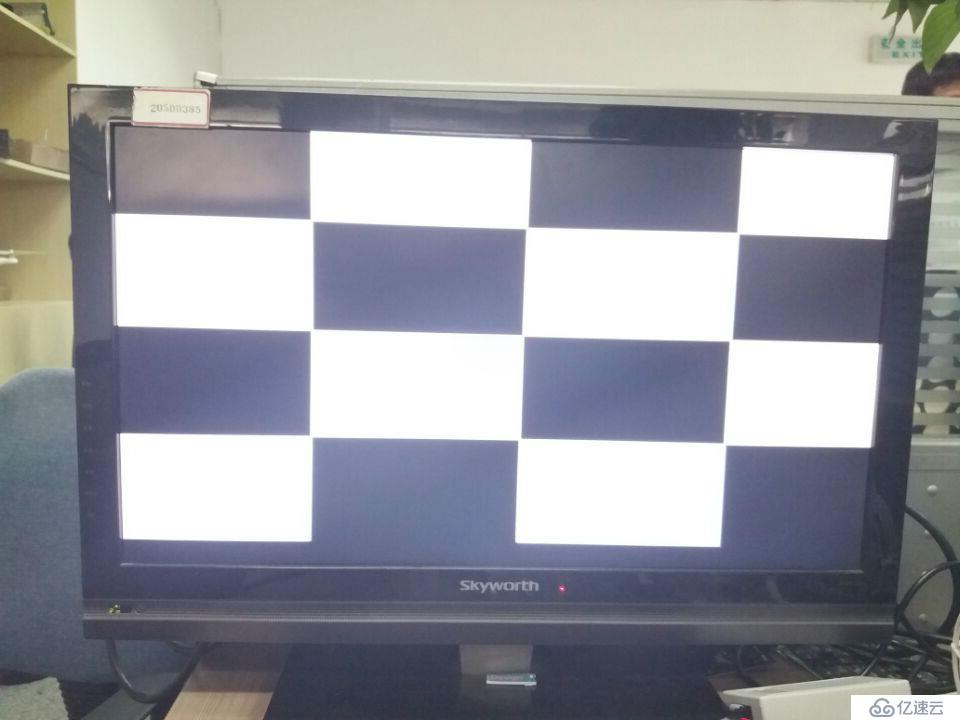

5.演示結果

下圖為方格顯示效果:

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。