您好,登錄后才能下訂單哦!

您好,登錄后才能下訂單哦!

Xilinx中的Primitives和Macros該怎么理解,針對這個問題,這篇文章詳細介紹了相對應的分析和解答,希望可以幫助更多想解決這個問題的小伙伴找到更簡單易行的方法。

源語(Primitives)-Xilinx庫中最簡單的設計元素。Primitives 基元是設計元素“原子”。Xilinx原語的示例包括簡單緩沖區BUF和帶有時鐘使能和清除功能的D觸發器FDCE。

宏(Macros)-Xilinx庫的設計元素“分子”。可以從設計元素原語或宏創建宏。例如,FD4CE觸發器宏是4個FDCE原語的組合。

Xilinx的原語分為10類,包括:計算組件,IO端口組件,寄存器/鎖存器,時鐘組件,處理器組件,移位寄存器,配置和檢測組件,RAM/ROM組件,Slice/CLB組件,G-tranceiver。具體原語資源更詳盡描述請參考文檔UG799以及UG768。

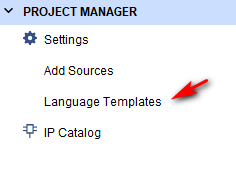

1>打開PROJECT MANAGER-->Language Templates

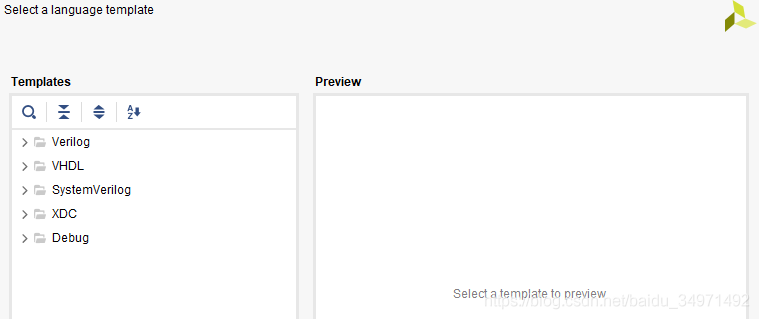

2>語言模板如下圖5大部分

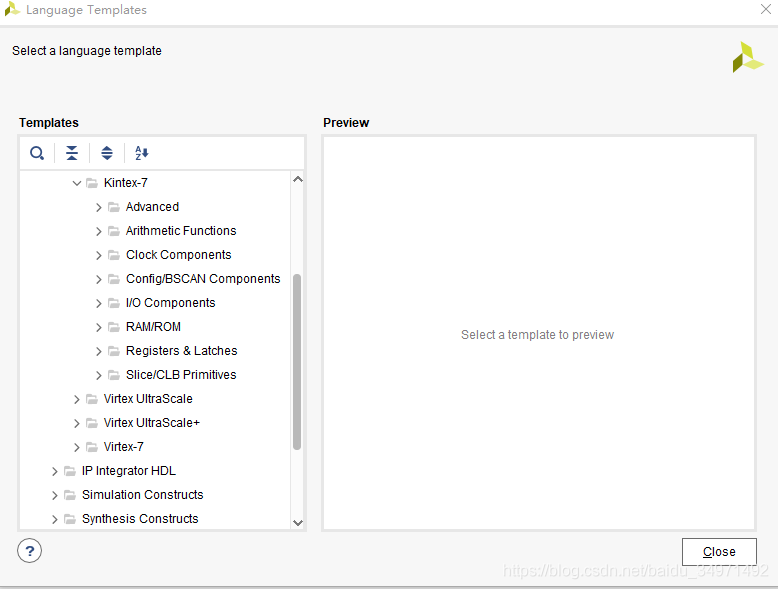

3>選擇相應的器件類型和模塊組件。

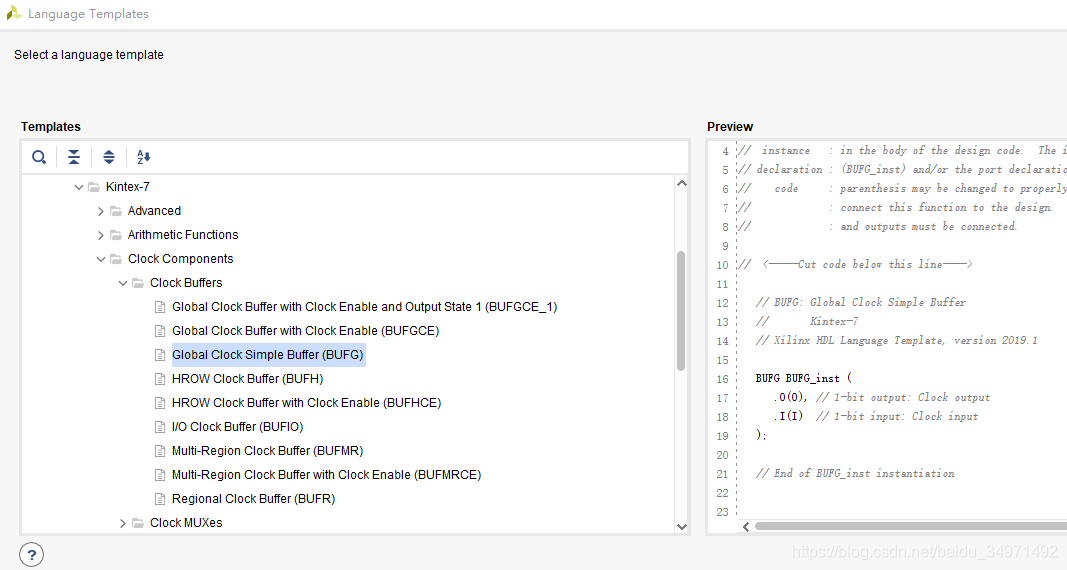

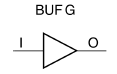

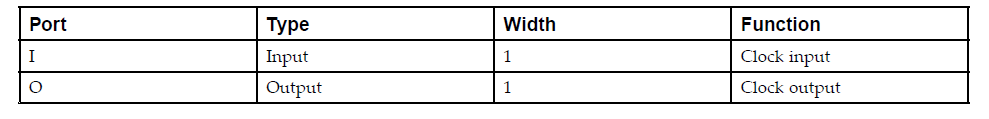

4>BUFG示例

// BUFG : In order to incorporate this function into the design,

// Verilog : the following instance declaration needs to be placed

// instance : in the body of the design code. The instance name

// declaration : (BUFG_inst) and/or the port declarations within the

// code : parenthesis may be changed to properly reference and

// : connect this function to the design. All inputs

// : and outputs must be connected.

// <-----Cut code below this line---->

// BUFG: Global Clock Simple Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2019.1

BUFG BUFG_inst (

.O(O), // 1-bit output: Clock output

.I(I) // 1-bit input: Clock input

);

// End of BUFG_inst instantiation

Primitive: Global Clock Simple Buffer

介紹:

該設計元素是一個高扇出緩沖器,可將信號連接到全局路由資源,以實現信號的低偏斜分布。BUFG通常用于時鐘網絡以及其他高扇出網絡,如置位/復位和時鐘使能。

端口描述:

關于Xilinx中的Primitives和Macros該怎么理解問題的解答就分享到這里了,希望以上內容可以對大家有一定的幫助,如果你還有很多疑惑沒有解開,可以關注億速云行業資訊頻道了解更多相關知識。

免責聲明:本站發布的內容(圖片、視頻和文字)以原創、轉載和分享為主,文章觀點不代表本網站立場,如果涉及侵權請聯系站長郵箱:is@yisu.com進行舉報,并提供相關證據,一經查實,將立刻刪除涉嫌侵權內容。